## **PC Power Supply Supervisor**

#### **General Description**

R7510A is a supervisor IC especially designed for PC power supplies with 3.3V, 5V and 12V outputs. The R7510A integrates a remote ON/OFF control input (PSONB), noise de-bounce/deglitch circuits, timing-and-fault control logics, an output power good indicator (PGO), an input power good input (PGI) and full output protections which include a fault indicator (FPOB), under voltage and over voltage protections. R7510A minimizes external component count and makes the designs of power supply easier.

As the PSONB receives a valid ON/OFF signal from a PC motherboard, the FPOB voltage goes low to start a poweron process. When the power-on process is completed, all of protections are enabled and the PGO voltage goes high to indicate that the output voltages are all in regulation ranges.

#### **Ordering Information**

R7510A口口

– Package Type N : DIP-8

Lead Plating System

G : Green (Halogen Free and Pb Free)

Note :

Richtek products are :

- RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- Suitable for use in SnPb or Pb-free soldering processes.

### **Marking Information**

RichPower R7510A GNYMDNN R7510AGN : Product Number YMDNN : Date Code

#### Features

- VDD Under Voltage Lockout Protection

- Output Over Voltage Protections (OVP) for 3.3V, 5V and 12V

- Output Under Voltage Protections (UVP) for 3.3V and 5V

- Open-Drain Power Good (PGO) and Fault Protection (FPOB) Outputs

- 300ms Power Good Delay Time

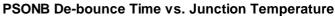

- 38ms PSONB Remote ON/OFF De-bounce Time

- 55µs OVP and 73µs UVP Noise Deglitch Times

- 3.5ms PSONB Turn-off Delay Time

- Two-Threshold PGI Input with 73µs Noise Deglitch Time

- 75ms UVP Blanking Time during Start-up

- Low Cost and Component Count

- RoHS Compliant and Halogen Free

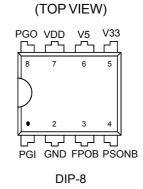

### **Pin Configuration**

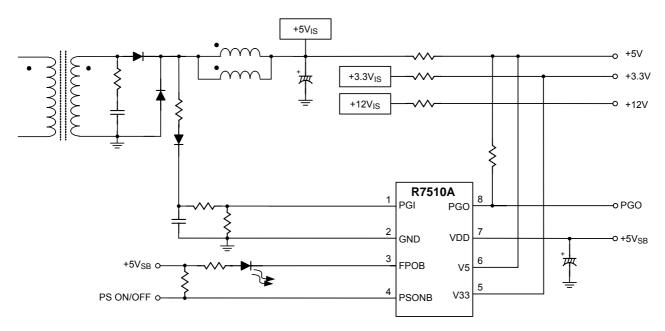

### **Typical Application Circuit**

### **Functional Pin Description**

| Pin No. | Pin Name | Pin Description                                                                                                                                         |

|---------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | PGI      | Power Good Signal Input Pin. This pin senses partial voltage of the system input voltage.                                                               |

| 2       | GND      | Ground Pin of the IC. All voltage levels are measured with respect to this pin. Ties the pin directly to system ground plane with the lowest impedance. |

| 3       | FPOB     | Fault Protection Output Pin. This pin is pulled low when PSONB = L and no protections happened.                                                         |

| 4       | PSONB    | Remote ON/OFF Control Input Pin. This pin is designed with a 38ms (typical) De-bounce time to avoid input voltage bounce.                               |

| 5       | V33      | 3.3V OVP and UVP Detection Input Pin.                                                                                                                   |

| 6       | V5       | 5V OVP and UVP Detection Input Pin.                                                                                                                     |

| 7       | VDD      | Supply Voltage and 12V OVP Detection Input Pin. Connect a noise decoupling capacitor between this pin and GND.                                          |

| 8       | PGO      | Open-Drain Power Good Output Pin. When all output voltages are in their regulation ranges, the PGO voltage goes high.                                   |

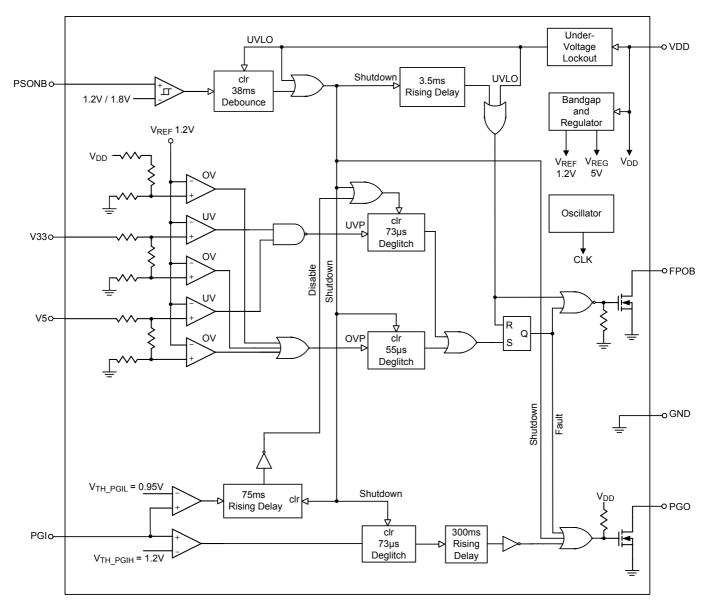

## Functional Block Diagram

#### **Functional Descriptions**

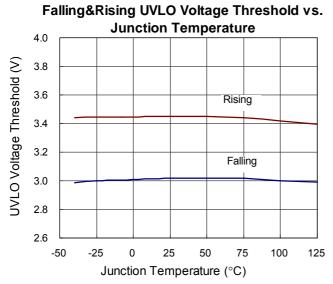

#### **VDD Under Voltage Lockout Protection**

The R7510A automatically initializes upon receipt of power. The Under Voltage Lockout (UVLO) function continually monitors the bias voltage at VDD pin. When the supply voltage ( $V_{DD}$ ) exceeds its rising UVLO threshold (3.6V typical), the IC is enabled to work. When the VDD voltage is under the UVLO voltage threshold (UVLO = H), the PGO voltage is pulled low to indicate the output voltages are not ready and the FPOB pin keeps high impedance to disable the primary-side PWM controller. The supply voltage must be below the absolute maximum rating for safety.

#### **Output Under Voltage Protection and PGI Input**

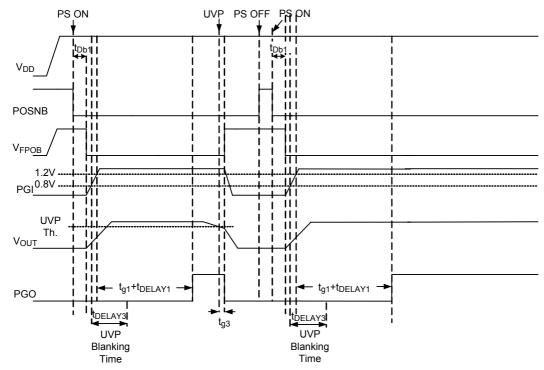

The R7510A provides under voltage protection for the 3.3V

and 5V outputs. The UVP continuously monitors the voltage on V33 and V5. When an under-voltage (UV) protection condition appears at one of the monitored pins for more than 73µs (typical) deglitch time, the PGO voltage goes low to indicate one of the output voltages is out of regulation. Meanwhile the FPOB also becomes high impedance to disable the primary-side PWM controller and protects the power supply system. The UVP protection condition is latched until PSONB is toggled from low to high or VDD restarts.

The UVP protection can be disabled by the PGI signal. During PSONB start-up or AC power-on, a UVP blanking signal disables the UVP detections to prevent wrong UVP. The blanking time is shown in the following table:

| IC     | Blanking Time | Start Condition          | Stop Condition           |

|--------|---------------|--------------------------|--------------------------|

| R7510A | 8             | V <sub>PGI</sub> < 0.95V | V <sub>PGI</sub> > 0.95V |

|        | 75ms          | V <sub>PGI</sub> > 0.95V | end of 75ms              |

The UVP protection is disabled when the PGI voltage keeps below the lower PGI voltage threshold 0.95V (typical). After the start-up is completed, the IC enters normal-mode operation. The UVP will be disabled when the PGI voltage falls below the lower voltage threshold 0.95V (typical). This function is designed to keep PWM switching and discharge the high-voltage charge in the bulk capacitors during AC power-off.

#### **Output Over Voltage Protection**

The R7510A has an output Over Voltage Protection (OVP) function, which monitors the 3.3V, 5V and 12V output voltages, to prevent power system and loads from damages during one or more output OV condition(s). The OVP starts monitoring the voltages on V33, V5 and VDD at end of the PSONB de-bounce time. When an Over Voltage (OV) condition appears at one of the monitored pins for more than the 55 $\mu$ s (typical) deglitch time, the PGO voltage goes low to indicate one of the output voltages is out of regulation. Meanwhile the FPOB also becomes high impedance to disable the primary-side PWM controller and protects the power supply system. The OVP condition is latched until PSONB is toggled from low to high or VDD restarts.

#### **PSONB De-bounce**

R7510A provides a remote ON/OFF control input pin (PSONB) for PC power supply applications. A built-in 38ms (typical) de-bounce circuit performs rising and falling edge noise de-bounce functions to identify valid PSONB input signals. The PSONB also has a TTL logic-compliant input voltage threshold and a hysteresis design against input noise.

#### **FPOB and PGO Outputs**

The FPOB and PGO are all open-drain output pins. The PGO voltage, pulled high by an external resistor connected to the 5V output, indicates the status of the outputs. The PGO keeps at low state, when VDD voltage<UVLO threshold, PSONB = H, PGI voltage<1.2V or one of the faults, including UVP and OVP occurs.

In general, the FPOB pin is used to enable the primaryside PWM controller via an opto-coupler. An external series resistor is used to limit the current flowing through the opto-coupler and FPOB pin. The FPOB keeps high impedance, when VDD voltage<UVLO threshold, PSONB = H or one of the faults, including UVP and OVP occurs.

#### **Function Table**

| Input Signals PGI PSONB  |   | Eve         | nts         | Output Signals |     |

|--------------------------|---|-------------|-------------|----------------|-----|

|                          |   | UV Detected | OV Detected | FPOB           | PGO |

| V <sub>PGI</sub> < 0.95V | L | No          | No          | L              | L   |

| V <sub>PGI</sub> < 0.95V | L | No          | Yes         | Н              | L   |

| V <sub>PGI</sub> < 0.95V | L | Yes         | No          | L              | L   |

| V <sub>PGI</sub> < 0.95V | L | Yes         | Yes         | Н              | L   |

| V <sub>PGI</sub> > 0.95V | L | No          | Yes         | Н              | L   |

| V <sub>PGI</sub> > 0.95V | L | Yes         | No          | Н              | L   |

| V <sub>PGI</sub> > 0.95V | L | Yes         | Yes         | Н              | L   |

| V <sub>PGI</sub> > 1.2V  | L | No          | No          | L              | Н   |

| X                        | Н | Х           | X           | Н              | L   |

Note: X = Don't care

FPOB = "L" means fault isn't latched

FPOB = "H" means fault is latched

PGO = "L" means fault

PGO = "H" means No fault

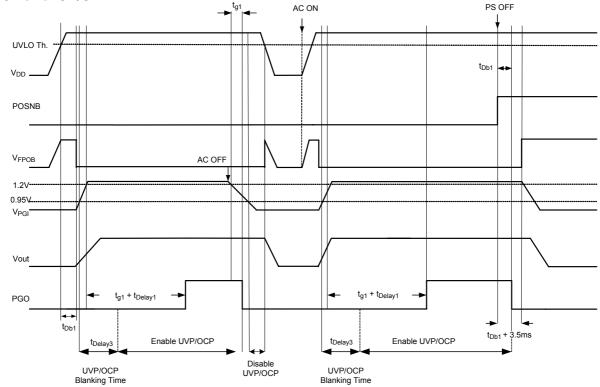

### **Timing Diagram**

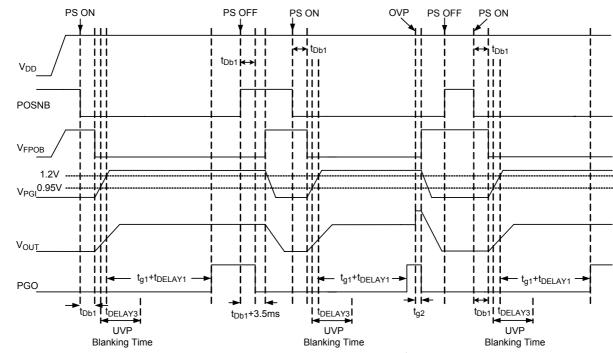

#### (1) AC Power ON/OFF

Note : PSONB = L  $\rightarrow$  AC Power-OFF  $\rightarrow$  AC Power-ON  $\rightarrow$  PSONB = H.

#### (2) PS ON/OFF and OVP

Note : PSONB = L  $\rightarrow$  PSONB = H  $\rightarrow$  PSONB = L  $\rightarrow$  OVP Latch  $\rightarrow$  PSONB = H  $\rightarrow$  PSONB = L.

#### (3) UVP

Note : PSONB = L  $\rightarrow$  UVP Latch $\rightarrow$  PSONB = H $\rightarrow$  PSONB = L.

## R7510A

### Absolute Maximum Ratings (Note 1)

| <ul> <li>VDD Supply Voltage (VDD to GND), V<sub>DD</sub></li></ul> |                |

|--------------------------------------------------------------------|----------------|

| FOI, PGO, PSONB, V3, V33 to GND voitage     FPOB to GND voltage    |                |

| • Power Dissipation, $P_D @ T_A = 25^{\circ}C$                     |                |

| DIP-8                                                              | 0.714W         |

| Package Thermal Resistance (Note 2)                                | 4.4000.000     |

| DIP-8, θ <sub>JA</sub> (Soldering, 10 sec.)                        |                |

| Lead temperature (Soldening, 10 sec.)     Junction Temperature     |                |

| Storage Temperature Range                                          | –65°C to 150°C |

| ESD Susceptibility (Note 3)                                        |                |

| HBM (Human Body Mode)                                              | 2kV            |

### Recommended Operating Conditions (Note 4)

| • | VDD Supply Voltage Range, V <sub>DD</sub> | 4V to 15V      |

|---|-------------------------------------------|----------------|

| • | Junction Temperature Range                | –40°C to 125°C |

| • | Ambient Temperature Range                 | –40°C to 85°C  |

#### **Electrical Characteristics**

(V<sub>DD</sub> = 5V, T<sub>A</sub> = 25°C, unless otherwise specified)

| Parameter                                           | Symbol                | Test Conditions                       | Min   | Тур  | Мах   | Unit |

|-----------------------------------------------------|-----------------------|---------------------------------------|-------|------|-------|------|

| VDD Supply Current and Under Voltage Lockout (UVLO) |                       |                                       |       |      |       |      |

| VDD Supply Voltage Range                            | V <sub>DD</sub>       | $T_A = -40^{\circ}C$ to $85^{\circ}C$ | 4     |      | 15    | V    |

| VDD Supply Current                                  | I <sub>DD</sub>       | V <sub>PSONB</sub> = 5V               |       | 0.5  | 1     | mA   |

| VDD Supply Current                                  |                       | V <sub>PSONB</sub> = 0V               |       |      | 3     | mA   |

| Rising UVLO Voltage Threshold                       | VTH_UVLOR             | V <sub>DD</sub> rising                | 3.2   | 3.4  | 3.6   | V    |

| Falling UVLO Voltage Threshold                      | VTH_UVLOF             | V <sub>DD</sub> falling               | 2.8   | 3    | 3.2   | V    |

| Over Voltage Protection Sectio                      | n (OVP)               |                                       |       |      |       |      |

| V33 Over Voltage Threshold                          | V <sub>TH_V33OV</sub> |                                       | 3.7   | 3.9  | 4.1   | v    |

| voo over vollage miesnolu                           |                       | $T_A = -40^{\circ}C$ to $85^{\circ}C$ | 3.66  | 3.9  | 4.14  |      |

| V5 Over Veltage Threshold                           | V <sub>TH_V5OV</sub>  |                                       | 5.7   | 6.1  | 6.2   | V    |

| V5 Over Voltage Threshold                           |                       | $T_A = -40^{\circ}C$ to $85^{\circ}C$ | 5.64  | 6.1  | 6.26  |      |

| VDD Quer Veltage Threehold                          | VTH_V12OV             |                                       | 12.9  | 13.4 | 13.9  | v    |

| VDD Over Voltage Threshold                          |                       | $T_A = -40^{\circ}C$ to $85^{\circ}C$ | 12.76 | 13.4 | 14.04 |      |

| Under Voltage Protection (UVP)                      |                       |                                       |       |      |       |      |

| V/22 Lindor Voltago Throshold                       | V <sub>TH_V33UV</sub> |                                       | 2     | 2.2  | 2.4   | v    |

| V33 Under Voltage Threshold                         |                       | T <sub>A</sub> = -40°C to 85°C        | 1.97  | 2.2  | 2.43  |      |

| Parameter                         | Symbol                | Test Conditions                          | Min                     | Тур                       | Max                     | Unit |

|-----------------------------------|-----------------------|------------------------------------------|-------------------------|---------------------------|-------------------------|------|

| \/F   Index \ /altaga Threehold   | \/                    |                                          | 3.3                     | 3.5                       | 3.7                     | - V  |

| V5 Under Voltage Threshold        | Vth_v5uv              | T <sub>A</sub> = -40°C to 85°C           | 3.26                    | 3.5                       | 3.74                    |      |

| V33 Pin Input Resistance          |                       |                                          |                         | 150                       |                         | kΩ   |

| V5 Pin Input Resistance           |                       |                                          |                         | 300                       |                         | kΩ   |

| PGO and FPOB Outputs              |                       |                                          |                         |                           |                         |      |

| PGO Leakage Current               | I <sub>LK_PGO</sub>   | $V_{PGO}$ = 5V, the internal NMOS is off |                         |                           | 5                       | μA   |

| PGO Low-level Output Voltage      | V <sub>OL_PGO</sub>   | I <sub>SINK</sub> = 10mA                 |                         | 0.23                      | 0.3                     | V    |

| PGO Rising Time                   | t <sub>R_PGO</sub>    | Pull-up Resistance = $1k\Omega$          |                         |                           | 100                     | ns   |

| FPOB Leakage Current              | I <sub>LK_FPOB</sub>  | V <sub>FPOB</sub> = 5V,<br>PSONB = Open  |                         |                           | 5                       | μA   |

| FPOB Low-level Output<br>Voltage  | V <sub>OL_FPOB</sub>  | I <sub>SINK</sub> = 10mA                 |                         | 0.2                       | 0.3                     | V    |

| PGI and PSONB Input               |                       |                                          |                         |                           |                         |      |

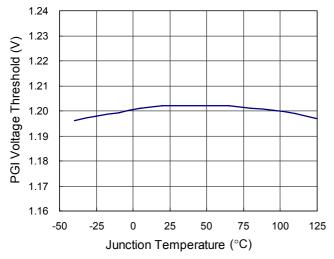

| Higher PGI Voltage Threshold      | V <sub>TH_PGIH</sub>  | (Note 5)                                 | 1.16                    | 1.2                       | 1.24                    | V    |

| Lower PGI Voltage Threshold       | $V_{TH_PGIL}$         | (Note 6)                                 | 0.9                     | 0.95                      | 1                       | V    |

| PGI Input Current                 |                       | V <sub>PGI</sub> = 1.2V                  |                         |                           | 1                       | μA   |

| PSONB Input Pull-up Resistor      | R <sub>PU_PSONB</sub> |                                          |                         | 26                        | 1                       | kΩ   |

| PSONB Input Pull-up Voltage       | V <sub>PU_PSONB</sub> |                                          |                         | 4.5                       |                         | V    |

| PSONB High-level Input<br>Voltage | VIH_PSONB             |                                          | 1.8                     |                           | -                       | V    |

| PSONB Low-level Input<br>Voltage  | VIL_PSONB             |                                          |                         |                           | 1.2                     | V    |

| Timing Characteristics            |                       |                                          |                         |                           |                         |      |

| PSONB De-bounce Time              | t <sub>Db1</sub>      |                                          | 26                      | 38                        | 50                      | ms   |

| PGI to PGO Deglitch Time          | t <sub>g1</sub>       | Rising V <sub>PGI</sub> > 1.2V           | 46                      | 73                        | 100                     | μS   |

| PGI to PGO Delay Time             | t <sub>DELAY1</sub>   | Rising V <sub>PGI</sub> > 1.2V           | 200                     | 300                       | 400                     | ms   |

| OVP Deglitch Time                 | t <sub>g2</sub>       | V <sub>V33/V5/VDD</sub> rising           | 35                      | 55                        | 75                      | μS   |

| UVP Deglitch Time                 | tg3                   | V <sub>V33/V5/V12</sub> falling          | 46                      | 73                        | 100                     | μS   |

| PSONB Turn-Off Delay Time         | t <sub>DELAY2</sub>   | from PSONB goes low to<br>FPOB goes high | 2 +<br>t <sub>Db1</sub> | 3.5 +<br>t <sub>Db1</sub> | 5 +<br>t <sub>Db1</sub> | ms   |

| UVP Power-On Blanking Time        |                       | V <sub>PGI</sub> < 0.95V                 |                         | Disable                   |                         |      |

|                                   | tDELAY3               | V <sub>PGI</sub> > 0.95V                 | 50                      | 75                        | 100                     | ms   |

## R7510A

- **Note 1.** Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured in the natural convection at  $T_A = 25^{\circ}C$  on a low effective single layer thermal conductivity test board of JEDEC 51-3 thermal measurement standard.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

- **Note 5.** The PGO is allowed to indicate the output statuses when PGI voltage rises above this voltage threshold; otherwise the PGO is held at low state.

- **Note 6.** This voltage threshold is used to start the UVP blanking time (75ms, when V<sub>PGI</sub> > 0.95V) and then enable the UVP during power-on. During normal operation, if the PGI voltage is below the threshold, the UVP is disabled.

### Typical Operating Characteristics

PGI Voltage Threshold vs. Junction Temperature

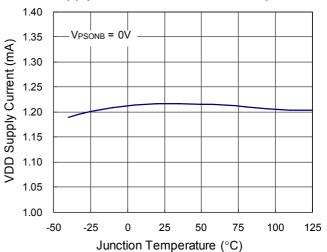

VDD Supply Current vs. Junction Temperature

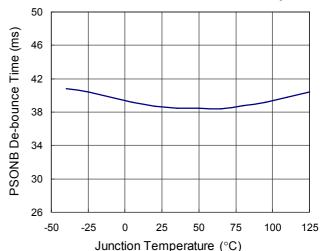

#### **Outline Dimension**

| Sumbol | Dimensions I | n Millimeters | Dimensions In Inches |       |  |

|--------|--------------|---------------|----------------------|-------|--|

| Symbol | Min          | Max           | Min                  | Max   |  |

| А      | 9.068        | 9.627         | 0.357                | 0.379 |  |

| В      | 6.198        | 6.604         | 0.244                | 0.260 |  |

| С      | 3.556        | 4.318         | 0.140                | 0.170 |  |

| D      | 0.356        | 0.559         | 0.014                | 0.022 |  |

| E      | 1.397        | 1.651         | 0.055                | 0.065 |  |

| F      | 2.337        | 2.743         | 0.092                | 0.108 |  |

| I      | 3.048        | 3.556         | 0.120                | 0.140 |  |

| J      | 7.366        | 8.255         | 0.290                | 0.325 |  |

| L      | 0.381        |               | 0.0                  | )15   |  |

8-Lead DIP Plastic Package

#### **Richtek Technology Corporation**

5F, No. 20, Taiyuen Street, Chupei City Hsinchu, Taiwan, R.O.C. Tel: (8863)5526789

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.